本文主要介绍全志 T3 JLink 调试环境搭建,基于 ACOEGC_T3(PF) 硬件板卡,系统架构使用裸核 * 3 + SylixOS 的 AMP 模式。调试环境可通过 RealEvo-IDE 和 JLink V9 同时对 T3 的 4 个核进行调试。

一、搭建调试环境

1、安装 JLink 软件,这里安装的是 V645a;

2、修改安装目录下的 JLinkDevices.xml 文件,这里的路径为: D:\Program Files (x86)\SEGGER\JLink_V645a。在 DataBase 和 /DataBase 之间添加如下内容;

- <Device> <ChipInfo Vendor="Allwinner" Name="T3_CORE0" Core="JLINK_CORE_CORTEX_A7" JLinkScriptFile="Devices/ALLWIN/T3/Core0.JLinkScript"/> </Device> <Device> <ChipInfo Vendor="Allwinner" Name="T3_CORE1" Core="JLINK_CORE_CORTEX_A7" JLinkScriptFile="Devices/ALLWIN/T3/Core1.JLinkScript"/> </Device> <Device> <ChipInfo Vendor="Allwinner" Name="T3_CORE2" Core="JLINK_CORE_CORTEX_A7" JLinkScriptFile="Devices/ALLWIN/T3/Core2.JLinkScript"/> </Device> <Device> <ChipInfo Vendor="Allwinner" Name="T3_CORE3" Core="JLINK_CORE_CORTEX_A7" JLinkScriptFile="Devices/ALLWIN/T3/Core3.JLinkScript"/> </Device>

3、在 JLink 安装目录下创建目录:JLink_V645a\Devices\ALLWIN\T3,在目录中放入脚本文件 Core0.JLinkScript、Core1.JLinkScript、Core2.JLinkScript、Core3.JLinkScript(见附件);

4、将 JLink V9 调试器接入板卡调试口(这里使用 JTAG 接口,也支持 SWD 接口),如下图所示。

二、RealEvo-IDE 调试配置

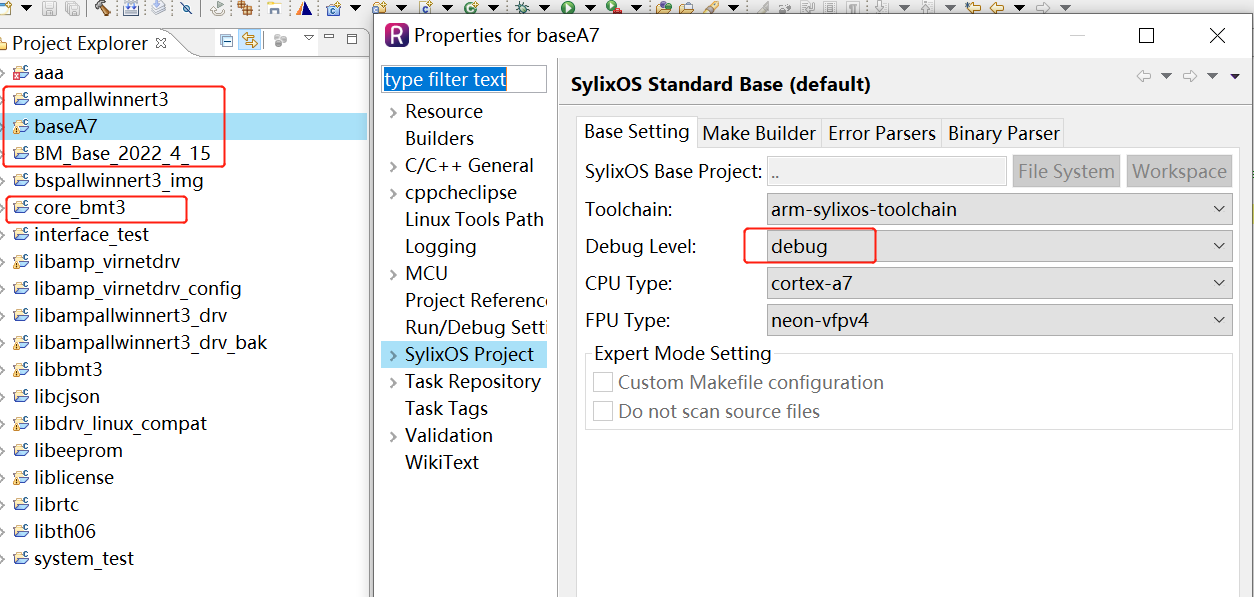

1、将裸核与系统核的 Base 和 BSP 改为 Debug 模式,重新编译;

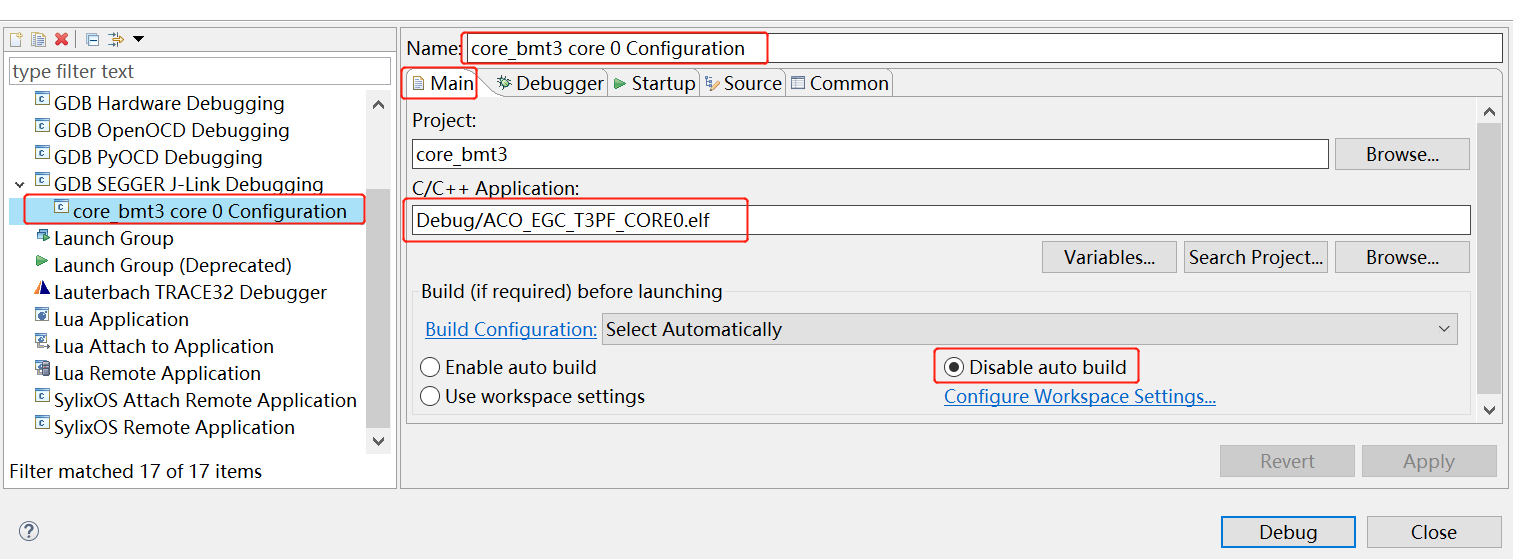

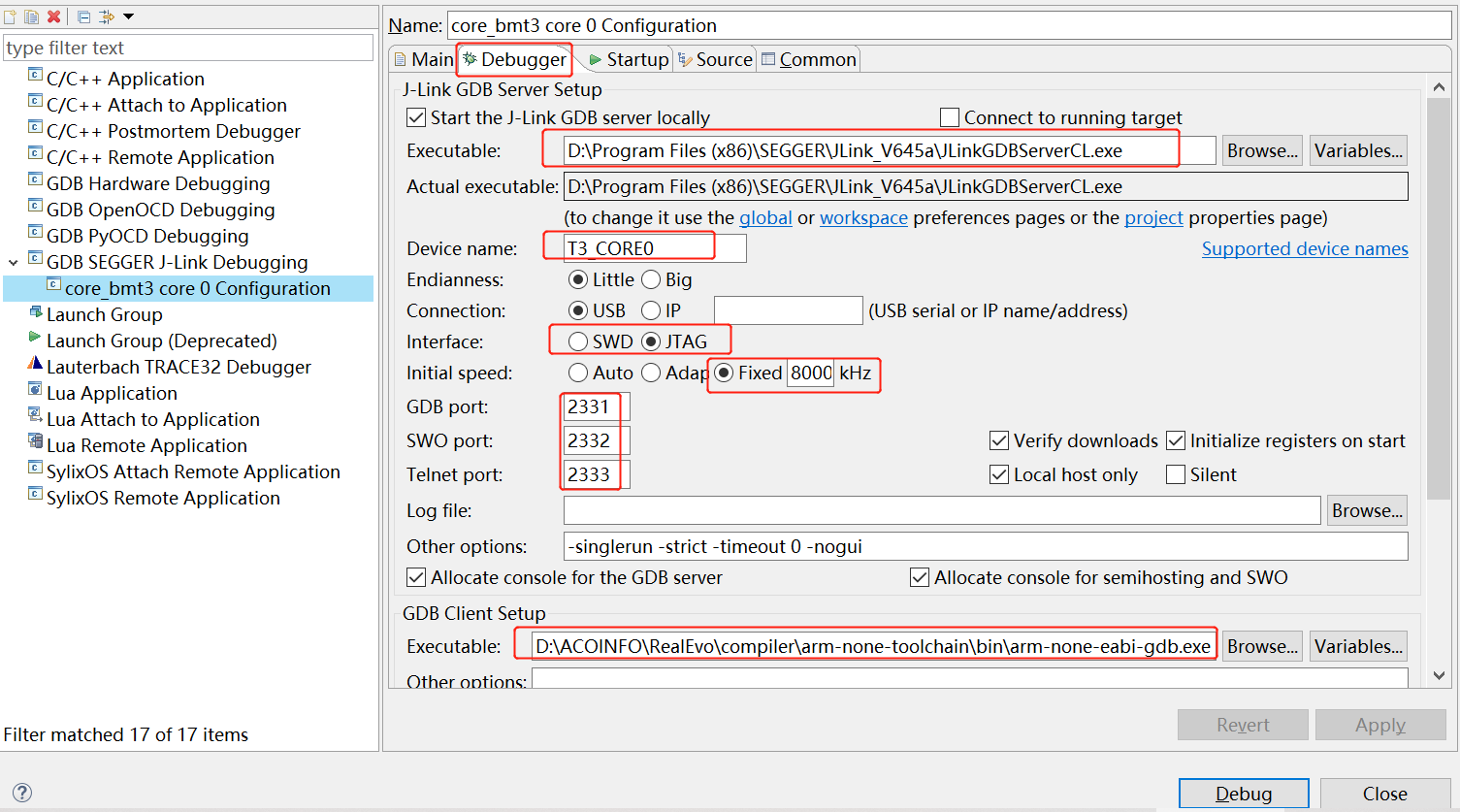

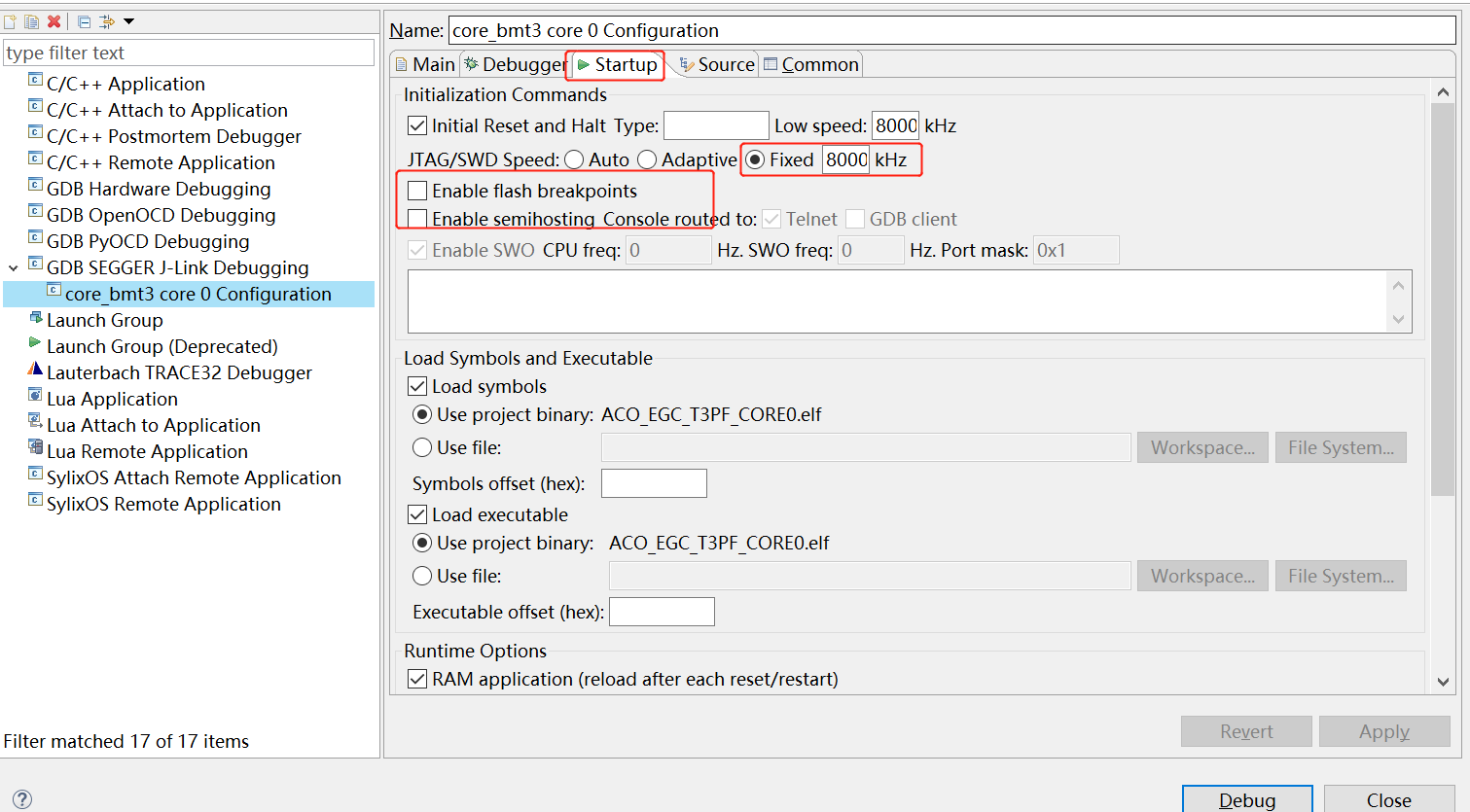

2、右键 core_bmt3 工程,点击 Debug As ---> Debug Configurations... 双击 GDB SEGGER J-Link Debugging 新建一个调试实例。配置 core0 调试参数,如下图:

3、使用同样的方式创建 core1 的调试实例,配置如下所示,注意 Device name 、端口号的变化:

4、使用同样的方式创建 core2 的调试实例,配置如下所示,注意 Device name 、端口号的变化:

5、右键 ampallwinnert3 工程,点击 Debug As ---> Debug Configurations... 双击 GDB SEGGER J-Link Debugging 新建一个调试实例。配置 core3 调试参数,如下图:

三、调试流程

1、系统上电后在裸核串口(UART0)上敲回车进入 u-boot 界面:

2、键入如下命令加载系统镜像:

- fatload mmc 2:2 0x40000000 ACO_EGC_T3PF_CORE0.bin;fatload mmc 2:2 0x50000000 ACO_EGC_T3PF_CORE1.bin;fatload mmc 2:2 0x58000000 ACO_EGC_T3PF_CORE2.bin;fatload mmc 2:2 0x60100000 ampallwinnert3_ACO_EGC_T3PF_bare_sys1.bin;

注意带 FPGA 版本这里还需要加入 FPGA 镜像加载命令:run loadfpga

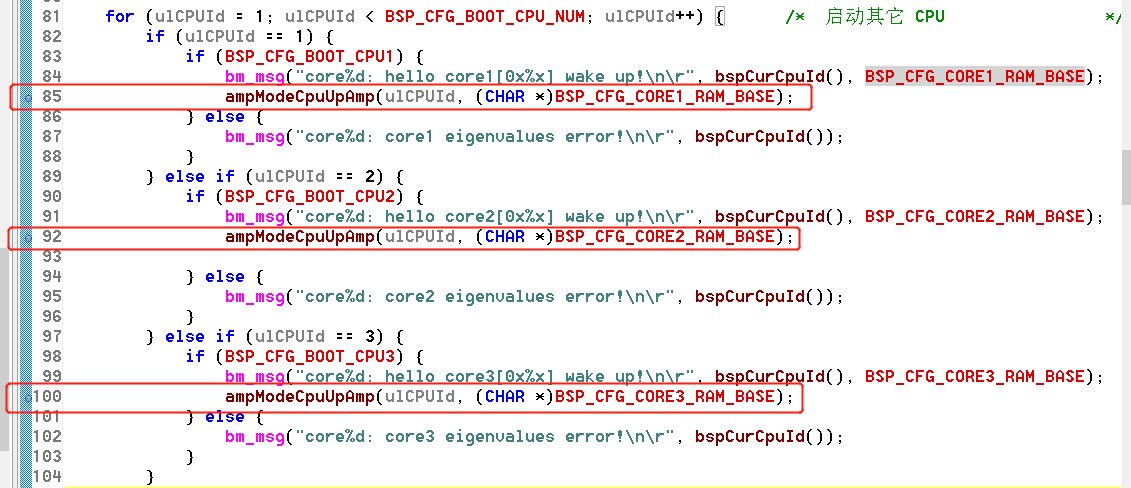

3、在代码 core_bmt3/SylixOS/bsp/bspInit.c 中的函数 halWakeUpOtherCores() 内启动核 1/2/3 的位置上加上断点  打开调试配置界面,调试 core0

打开调试配置界面,调试 core0

4、全速运行到第一个断点处,下一步执行启动 core1,执行后用同样的方法打开 core1 的调试界面并启动调试

成功启动后出现如下信息:

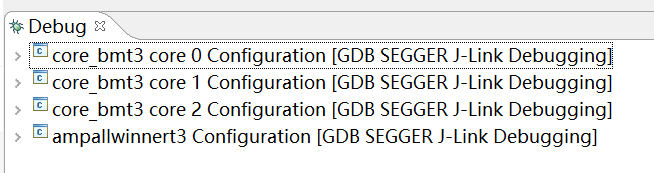

5、使用同样的方式启动 core2 和 core3,4 个核都启动后可以通过 Debug 窗口切换调试对象,从而实现 4 核同时调试。

四、其他

1、这里仅介绍 4 核同时调试的情况,实际使用中可根据需要调试指定核即可;

2、JLink 若采用 SWD 连接方式则调试接口配置也需要改为 SWD: